재미삼아 써봤는데 내가 이쪽 업계가 아닌지라 틀릴수 있음

1. 적층형 센서의 장점?

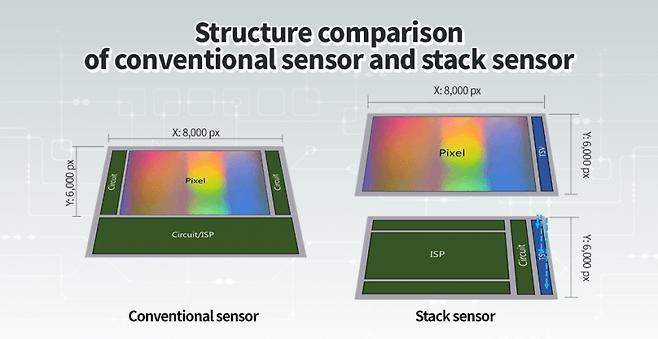

비적층형 센서의 경우 circuit/image signaling processor(isp) 등등이 Pixel 바로 옆에 붙어있지만

적층형 센서의 경우 isp와 서킷을 pixel 밑에 적층을 시키기 때문에 센서 부품의 크기를 줄이거나 같은 크기라면 픽셀 크기나 화소를 키울 수 있음

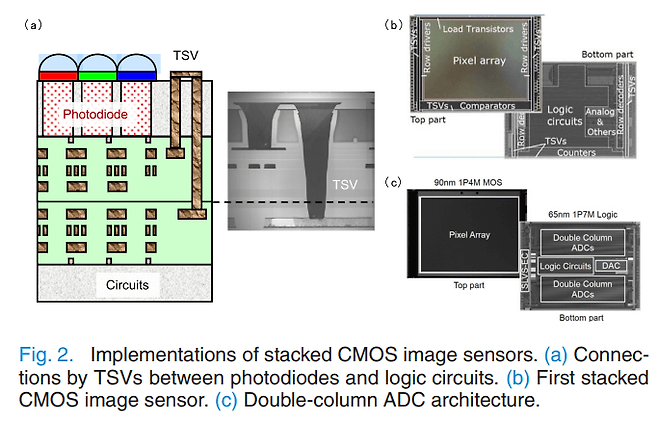

그렇기 때문에 부품사이즈에 민감한 스마트폰 등에서는 2012년부터 상용화된 기술이고 상대적으로 부품 사이즈에

덜 민감하고 돈이 안되는 크롭이상 카메라 사업부에서는 상대적으로 늦게 도입되었음

2. 적층형 센서의 단점?

하지만 적층형에서는 장점만 있는건 아님

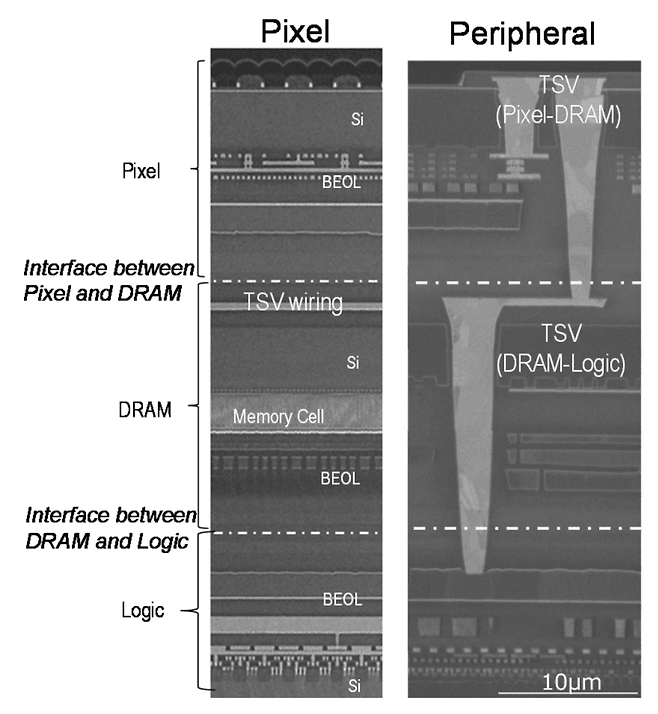

결국 적층을 하기 때문에 물리적으로 상단의 픽셀과 하부의 로직 사이를 연결해주는 TSV라는 회로가 필요하게 되는데

이 회로가 추가됨으로써 parasitic capacitance가 존재하고 그 결과 리드아웃 과정에서 노이즈가 생길 수 밖에 없음

3. 단점을 해결해볼까?

하지만 과학자들과 엔지니어는 멍청하지않음

픽셀과 로직이 분리되었기 때문에 각각을 최적화해서 노이즈를 줄여 보면 안될까? 라는 생각을 엔지니어들이 하게되었고

구형 Dram 공정을 신형 Dram 공정으로 대체하는 과정에서 삼성전자와 하이닉스는 밑의 로직 회로를 dram에서는 도태되었지만 CMOS 업계에서는 충분히 훌륭한 구형 공정으로 성능을 향상시키자라고 결정했고

기존에는 픽셀도 65nm 로직도 65nm로 생산했다면, 픽셀은 65nm, 로직은 구형 dram 14nm 공정에서 생산한 다음 TSV로 엮어주는 과정으로 최대한 노이즈를 줄일려고 했음

그 결과 다양한 논문에서는 이러한 미세공정을 적극적으로 활용하면 기존 센서보다 고감도 성능이 우월해진다라고 결론 내렸음

4.거기서 한단계 더 나아가볼까?.

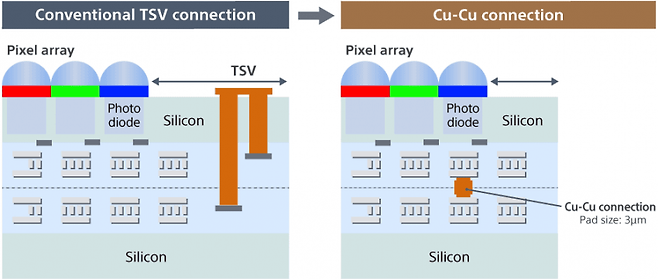

TSV의 단점을 해결하기 위해 회로끼리 구리-구리 커넥션으로 대체함으로써 노이즈도 줄이고 면적에서 손해도 덜보는 공정도 개발되었고.

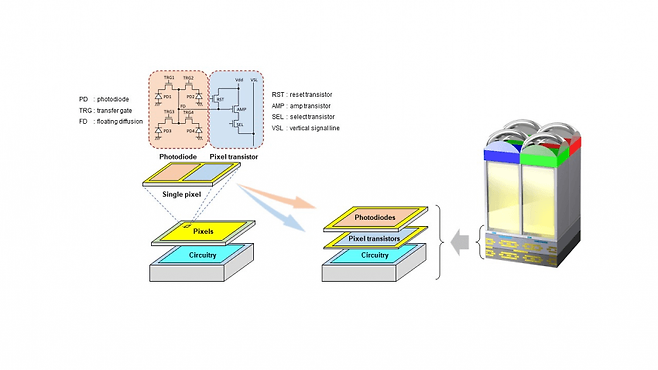

픽셀의 경우 Photodiode와 pixel transistor로 구성되서있는데

이러한 구조로 되어있으면 단점이 있음

제한된 크기에서 고감도 성능을 늘리기위해

Photodiode를 키우자니 pixel transistor가 줄어서 amp의 성능이 저하되고 Pixel transistor의 크기를 늘려서 amp의 성능을 키우자니 photodiode의 크기가 줄어들게됨

그래서 X니는 그럼 픽셀 트랜지스터도 분리해서 적층하는 신기술을 개발해냈고 픽셀 트랜지스터가 사라진 틈을 타 포토 다이오드의 크기를 늘렸고 픽셀 트랜지스터가 분리되어 적층되었으니 그럼 걔네도 미세공정으로 성능을 향상시키자 라는 생각을 했음

그결과 같은 센서 크기에서 포토다이오드의 전류가 두배 가량 증가하는 엄청난 향상을 이뤄냄

그외에도 VTG 등의 기술이 있지만 여기선 생략

결론 소니야 삼성아 하이닉스야 온세미야 열심히 하자

- dc official App