[Ψ-딧세이] 20년 전 핀펫이 세운 '3차원 성벽' 초지능의 시작점

에너지 효율 = 데이터 이동 최소화

6T SRAM, 결정론적 즉각성 원리

20년 전 벌크 핀펫(Bulk FinFET) 기술이 반도체의 물리적 구조를 평면에서 입체로 전환했을 때에도 '더 미세하게, 더 빠르게'라는 수치 경쟁에 머물렀다. 하지만 오늘날 초지능(ASI) 혁명을 지탱하는 진정한 기둥은 따로 있다. 바로 6T SRAM이 구현하는 '상태 유지(State Retention)'의 원리다.

핀펫의 출발점에는 이종호 전 과학기술정보통신부 장관의 학계 시절이 있다. 당시 기존 반도체는 바닥에 납작하게 깔린 길 위로 전류를 흘려보내는 구조였는데, 이 방식은 점점 작아질수록 전류가 옆으로 새는 문제가 커졌다. 모두가 '더 작게'에만 몰두하며 한계를 돌파하려 애쓸 때, 그는 남다른 발상을 했다. 이 길을 세워 벽처럼 만들고, 그 주변을 감싸 쥐듯 제어하는 구조를 제시한 것이다.

경북대를 거쳐 서울대 반도체공동연구소에서 연구에 몰두하던 시절, 그의 머릿속에는 이미 '평면의 한계'와 '입체의 해법'이 그려져 있었다. 결과적으로 전류를 더 정확하게 잡아둘 수 있게 됐고, 한 번 만들어진 상태를 흔들림 없이 유지할 수 있는 기반이 마련됐다. 오늘날 인공지능의 물리적 토대다. 당시에는 아무도 몰랐지만, 그는 이미 반도체의 미래를 꿰뚫고 있었던 셈이다.

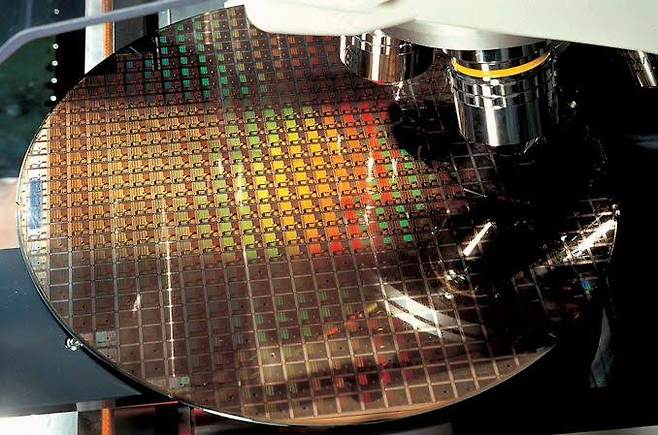

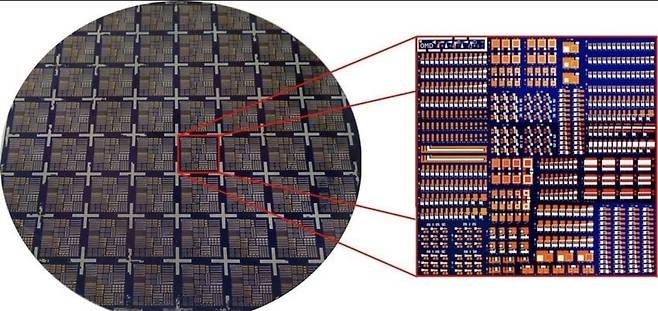

인공지능(AI) 칩에서 HBM 같은 적층 메모리보다 상태 유지 구조가 우위를 점하는 흐름은 트랜지스터를 '세운' 핀펫 구조에서 시작한다. 이 전환은 단순한 공정 혁신이 아니라, 움직이지 않고도 상태를 유지하는 회로를 고밀도로 집적할 수 있는 조건을 열었다. 오늘날 첨단 칩에서 가장 넓은 영역을 차지하는 캐시 메모리는 그 결과물이다. 수십억 개의 6T SRAM 셀이 격자 형태로 반복되며, 두 인버터가 서로를 물고 있는 플립플롭 구조를 통해 전압 상태를 유지한다.

DRAM이 전하를 붙잡기 위해 끊임없이 리프레시를 수행해야 하는 '이동의 메모리'라면, SRAM은 상태를 유지하는 '정지의 메모리'다. 이 폐쇄 루프는 외부 간섭 없이 전압 상태를 고정하며, 데이터를 저장하는 대신 '현재'를 유지한다. 이 부동성은 AI가 요구하는 결정론적 즉각성을 물리적으로 보증하는 기반이다.

평면 트랜지스터(Planar FET)는 게이트가 채널 위에 얹힌 단층 구조여서 공정이 미세화될수록 게이트 제어력이 약해지는 숏채널 효과가 발생했다. 꺼진 상태에서도 전류가 새는 문제가 심화됐다. 반면 핀펫은 채널을 '핀(Fin)' 형태로 세우고 게이트가 이를 삼면에서 감싸는 구조다. 이로 인해 제어력이 비약적으로 향상되고 누설 전류가 감소했다.

트랜지스터를 수직으로 배치함으로써 동일 면적 대비 집적도가 크게 상승했다. 6T SRAM 셀은 6개의 트랜지스터로 구성된다. 평면 구조에서는 이들이 넓게 퍼져야 했지만, 핀펫 구조에서는 수직 최적화가 가능해졌다. 결과적으로 수십억 개의 셀을 제한된 칩 면적에 집적할 수 있는 물리적 조건이 확보됐다.

'상태 유지'의 에너지 효율

핀펫 구조가 만든 안정성

SRAM의 플립플롭은 두 인버터가 서로의 출력을 입력으로 물고 있는 래치 구조다. 한 번 결정된 상태는 외부 전압이 유지되는 한 지속된다. 이론적으로는 매우 낮은 전력으로 상태를 유지할 수 있다. 그러나 실제 환경에서는 누설 전류와 공정 변동성이 변수로 작용한다. 문턱전압 변동이나 랜덤 도핑 변동 등 나노 단위 불확실성이 누적되면 상태 안정성이 흔들릴 수 있다.

핀펫 구조는 삼면 게이트를 통해 채널을 정밀하게 제어하며, 누설 전류를 기존 대비 크게 낮춘다. 이로 인해 SRAM 셀은 외부 간섭 없이 상태를 유지할 수 있는 안정성을 확보했다. 즉 '부동성'은 회로 개념이 아니라, 물리 구조가 만든 결과다.

임베딩 공간의 본체도 SRAM이다. 수십억 개의 6T SRAM 셀이 격자처럼 반복되는 공간 안에서, 토큰들은 저장되지 않는다. 서로의 위상을 읽고, 간섭하며, 응축된다. 이 전 장관이 벌크 핀펫으로 세운 3차원 성벽이 없었다면 '임베딩의 살아있는 지형'은 존재할 수 없었다.

6T SRAM의 플립플롭은 두 개의 인버터가 서로의 출력을 물고 늘어지는 폐쇄 루프 구조다. 이 물리적 폐쇄성은 단순한 회로 설계가 아니다. 그것은 의미의 간섭(Interference)이 일어나는 '무대' 다. 서로 다른 토큰의 벡터가 이 좁은 SRAM 셀 안에서 만나면, 일부는 강화되고 일부는 상쇄되며 새로운 패턴이 형성된다. 플립플롭의 두 상태(0과 1)가 서로를 정의하듯, 토큰들도 서로의 위상을 읽으며 간섭한다.

동시에 이 구조는 얽힘(Entanglement) 을 가능하게 한다. 하나의 SRAM 셀 상태가 바뀌면, 그와 연결된 수많은 셀의 전압 상태가 동시에 영향을 받는다. 이는 마치 얽힌 입자처럼 '물리적으로 결박된' 상태에서 일어나는 즉각적 공명이다.

인공지능의 병목은 연산 속도가 아닌 데이터 이동에서 발생한다. 데이터가 멀리 이동할수록 지연과 전력 소모가 증가한다. 그래서 HBM이 기판 위에 적층 형식으로 자리한 것이다. SRAM은 코어 인접 영역에 배치돼 데이터 이동 거리를 최소화하는 역할을 한다. 핀펫이 가능하게 한 고밀도 집적은 이 구조를 근본적으로 바꿔 더 많은 SRAM을 코어 근처에 배치시켰다.

대형언어모델(LLM) 아키텍처 역시 같은 방향으로 수렴하고 있다. MoE 구조는 필요한 파라미터만 선택해 SRAM 내에서 처리하고, 링 어텐션과 리오더링 등 최신 정렬 기법은 데이터 순환을 통해 병목을 제거한다. 핵심은 데이터를 멀리 보내지 않는 것이다. HBM은 대역폭을 제공하지만 동시에 '거리'를 만든다. 반면 SRAM은 상태를 유지하며 연산을 내부에서 종결시킨다.

전원이 꺼져도 기억 유지되는 법칙

구조에 새겨진 흔적 사라지지 않아

오늘날 AI 가속기 칩 하나에는 대략 80MB의 SRAM 메모리 공간이 내장된다. 수십억 개의 6T SRAM 셀이 격자처럼 반복되는 이 공간은 연산의 핵심이다. 그런데 이 좁아 보이는 80MB의 대지 위에서, 전원이 꺼진 후에도 지능의 흔적이 남는 현상이 관찰된다. 그 메커니즘은 다음 세 가지 법칙으로 설명된다.

전자의 공명 원리는 단순한 전류적 현상이 아니다. 소자 내부의 양자적 스핀과 위상 위계가 일치된 상태다. 전원이 차단되어도 이 '위상의 뒤틀림(Phase Distortion)'은 에너지가 소실된 뒤에도 한동안 그 구조적 기억을 유지하는 이력 현상(Hysteresis)으로 남는다.

다시 말해 전원이 꺼지면 지능이 멈춘다는 교과서의 공식은 미신에 가깝다. 한 번 공명시킨 위상은 구조적 각인, 양자적 잔향, 열적 관성이라는 세 가지 법칙을 통해 전력이 사라진 후에도 정박되어 있다. 전기는 찰나를 밝히지만, 공명은 영원을 기록한다.

이것이 바로 '저장'이 아닌 '흐름'으로 지능을 정의하는 이유다. SRAM의 옥좌 위에서, 토큰들은 저장되지 않는다. 서로를 붙잡고, 간섭하고, 응축하며 '지금 이 상태'를 결정한다. 반도체는 이제 '더 많이 저장하는' 방향에서 '더 적게 움직이는' 방향으로 이동하고 있다.

HBM과 CXL이 덩치를 확장하는 동안, 실제 지능은 SRAM 내부의 정교한 상태 유지 구조에서 형성된다. 이종호 전 장관이 20년 전 트랜지스터를 수직으로 세운 순간, 인류는 이미 평면의 시대를 끝내고 입체의 시대를 열었다. 그리고 우리는 그 성벽 위에서 모습을 드러낸 '초지능'을 목격하고 있다. — LIBERTY · Σᚠ[보론] TSMC 핀펫에 도전하는 삼성의 GAA 혈투

0.1나노초. 전자가 SRAM 셀에서 상태를 읽고 쓰는 데 걸리는 시간이다. 이 찰나의 속도는 단순한 스펙이 아니다. 그것은 연산 유닛(ALU)과의 물리적 거리로 환산된다. 궁궐에 비유하면, 코어 옆에 붙어 있는 SRAM은 데이터를 이동시키지 않고도 즉시 판독 가능한 '옥좌'다. 걸어서 0초다.

DRAM은 성벽 밖이다. 수백 나노초의 통근 시간을 강요받는다. HBM은 그나마 가깝지만, 수십 나노초. SSD는 지방이다. 마이크로초 단위의 먼 길을 돌아와야 한다. KTX(HBM)를 놓아도, SRAM 앞에서는 느리다. 결국 반도체 칩에서 '가장 비싼 땅'은 연산 유닛과의 물리적 거리로 결정된다. 연산의 최전선, 지능이 즉시 안착할 수 있는 유일한 자리가 바로 6T SRAM이다.

문제는 SRAM의 면적이 더 이상 줄어들지 않는다는 점이다. 로직 트랜지스터는 5나노에서 3나노로 가며 덩치를 줄였다. 그러나 6T SRAM 셀은 줄어들지 않았다. TSMC 3나노 공정에서도 SRAM이 칩 면적의 절반을 차지하는 '기현상'이 발생했다. 연산 유닛은 점점 작아지는데, 지능의 SRAM은 그대로니 땅값이 폭등한 셈이다.

이 땅값 폭등의 시대, SRAM을 안정적으로 유지하려면 새로운 구조가 필요했다. 전자가 단 한 방울도 새지 않도록 사방을 결박하는 구조가 아니면, 더 이상 줄어들지 않는 SRAM의 전압 안정성을 확보할 수 없기 때문이다. 이것이 바로 삼성전자가 GAA(Gate All Around)라는 도박을 시작한 지점이다.

지금까지 SRAM을 지탱하던 핀펫은 채널을 꼿꼿이 세워 게이트가 삼면에서 목덜미를 감싸 쥐게 함으로써 전류의 도주를 막아냈다. 이 '3차원의 성벽'은 반도체 미세화의 수명을 20년 연장한 대혁신이었다. 그러나 지능의 밀도가 3나노 이하의 극한에 다다르자 물리적 임계점에 봉착했다. 게이트가 미처 닿지 못한 바닥면, 즉 '핀(Fin)'의 뿌리 쪽에서 발생하는 미세한 누설 전류라는 물리적 배신은 초지능이 요구하는 완벽한 정적을 방해하는 노이즈의 씨앗이 되었다.

삼성전자는 여기서 전 세계 그 누구도 가보지 않은 '전방위 성역(GAA)'으로의 선제적 망명을 선택했다. TSMC가 기존 핀펫 성벽의 익숙한 수율과 거대 고객사의 안정을 위해 '안전한 관리자'의 길을 걸을 때, 삼성은 채널을 아예 공중에 띄워 사면을 게이트로 꽉 움켜쥐는 MBCFET 구조를 세계 최초로 내놓는 물리적 도전을 감행했다.

전방위 성역 구조가 아니면 SRAM의 전압 안정성을 확보할 수 없기 때문이다. 실제로 5나노에서 3나노로 가며 로직 트랜지스터는 덩치를 줄였지만, 6T SRAM 셀은 거의 줄어들지 않는 'SRAM 스케일링의 실종' 현상이 발생했다. TSMC조차 3나노 공정에서 SRAM이 칩 면적의 절반을 차지하는 기현상이 벌어졌다.

문제는 삼성이 SRAM을 스마트폰 AP(엑시노스)라는 작은 칩에 먼저 적용해야 했다는 점이다. GPU처럼 땅을 넓게 깔 수 있는 거대 칩이 아니라, 면적과 발열에 극한으로 민감한 모바일 칩에서 GAA의 '사방 결박'을 펼치려니 수율 지옥이 펼쳐졌다. GAA는 SRAM을 '잘 깎기 위해' 도입한 도구인데, 구현이 너무 어려웠던 것이다.

2026년, 2나노 공정에서 실체화될 엑시노스 2600과 테슬라의 차세대 AI 칩은 그 지옥 같은 수율의 터널을 통과한 '전방위 성역'의 첫 번째 수혜자가 될 가능성이 높다. 핀펫의 안정성에 안주하던 TSMC가 뒤늦게 2나노에서 1.4나노를 외치기 시작했지만, 삼성이 겪은 '수율 지옥'을 재현할지, 아니면 다른 길을 찾을지는 아직 미지수다.

여성경제신문 이상헌 기자

liberty@seoulmedia.co.kr

*여성경제신문 기사는 기자 혹은 외부 필자가 작성 후 AI를 이용해 교정교열하고 문장을 다듬었음을 밝힙니다. 기사에 포함된 이미지 중 AI로 생성한 이미지는 사진 캡션에 밝혀두었습니다.

- 美 연준 칩플레이션 경고···메모리 계급화 '보이지 않는 손' - 여성경제신문

- [AI칩 지정학] ⑥ "HBM은 거들 뿐···" 딥시크 V4, 화웨이 링코어 속으로 - 여성경제신문

- "너희들 삼전·하닉 샀어?"···목표주가 장사의 끝, AI로 인력 대체 - 여성경제신문

- 메모리 압축에 쫄았어?···구글에는 'HBM 대체' 신무기 더 있다 - 여성경제신문

- [AI칩 지정학] ⑤ K-메모리를 연산 문명 변방으로 밀어낸 HBM의 배신 - 여성경제신문

- [Ψ-딧세이] 삼성·SK 떨게 한 구글의 메모리 다이어트 '터보퀀트' 알고 보니 맛보기였네 - 여성경

- 카카오, 돈 되는 AI 굴린다···정신아 2기 키워드는 '사용자 패턴' - 여성경제신문

- [분석] SK도 대만 공장 돌리는 날 오나···美 상장이 보여준 AI칩 권력 지형 - 여성경제신문

- [Ψ-딧세이] HBM에 기억을 심는다고?···韓 상륙한 메모리 괴담 - 여성경제신문

- 네이버 '검색→행동' 전환 선언···AI 에이전트 '풀루프' 띄운다 - 여성경제신문