삼성 파운드리, 글로벌 EDA 3사와 2나노 최적화

전체 맥락을 이해하기 위해서는 본문 보기를 권장합니다.

삼성전자가 2나노미터(㎚) 파운드리 공정(SF2·SF2P) 최적화를 위해 글로벌 전자설계자동화(EDA) 기업과 협력한다.

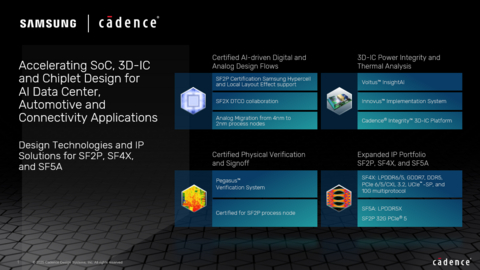

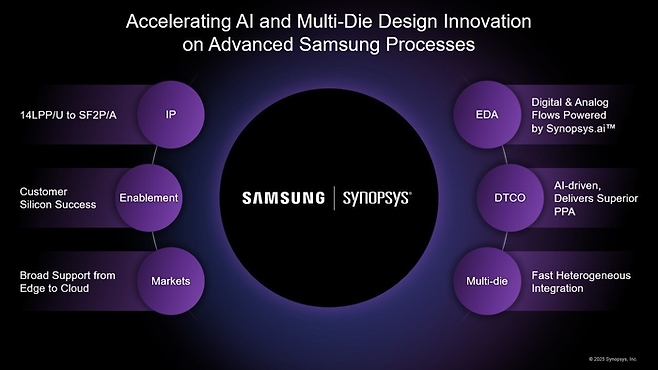

케이던스·시높시스·지멘스는 삼성 파운드리와 2나노 공정 기반의 설계 자동화, 반도체 설계자산(IP) 공급 확대, 전력 분석 및 검증 기술 등에서 공조한다고 최근 발표했다.

이외에도 삼성 파운드리는 EDA 3사와 실리콘 포토닉스 설계 검증, 고속 테스트와 결함 진단, 아날로그 회로의 신뢰성 분석 기술 등에 있어 협력한다.

이 글자크기로 변경됩니다.

(예시) 가장 빠른 뉴스가 있고 다양한 정보, 쌍방향 소통이 숨쉬는 다음뉴스를 만나보세요. 다음뉴스는 국내외 주요이슈와 실시간 속보, 문화생활 및 다양한 분야의 뉴스를 입체적으로 전달하고 있습니다.

삼성전자가 2나노미터(㎚) 파운드리 공정(SF2·SF2P) 최적화를 위해 글로벌 전자설계자동화(EDA) 기업과 협력한다.

케이던스·시높시스·지멘스는 삼성 파운드리와 2나노 공정 기반의 설계 자동화, 반도체 설계자산(IP) 공급 확대, 전력 분석 및 검증 기술 등에서 공조한다고 최근 발표했다.

EDA 3사는 삼성 파운드리의 SF2 또는 SF2P 공정에 최적화된 EDA 툴 인증을 완료했다. 일부 툴은 삼성이 개발한 '하이퍼 셀'과 '로컬 레이아웃 효과(LLE) 2.0' 기술을 지원해 설계 정확도를 높이고, 개발 기간을 줄이도록 했다.

또 다양한 IP 포트폴리오를 2나노를 비롯한 삼성 공정에 맞춰 제공한다. DDR5, LPDDR6, PCIe, UCIe, USB, MIPI 같은 고속 인터페이스와 자동차용 PHY, 보안 IP는 물론, 기존 아날로그 IP를 최신 공정에 맞게 빠르고 정확하게 옮기기 위한 이전 도구와 시뮬레이션·검증 솔루션도 포함된다.

삼성은 EDA 3사와 함께 첨단 2.5D, 3D 반도체 패키징 기술에서도 협력을 강화한다.

시높시스는 삼성의 '아이큐브(I-Cube) S' 2.5D 패키지 기술 기반으로 HBM3 스택 다이를 포함한 고객 설계를 성공적으로 테이프아웃 했으며, 자사의 3D-IC 컴파일러를 통해 TSV 설계와 열 분석, 범프 배치 최적화를 지원한다.

지멘스는 '칼리버 3D 스택' 툴을 활용해 실리콘 인터포저 기반 다이(Die) 간 안테나 효과와 정전기 방전(ESD) 검증 자동화를 개발했고, 케이던스는 전력 무결성 해석 솔루션을 통해 3D-IC 기반 고속 CPU 설계에서 전압 강하 문제를 80~90% 해결할 수 있다고 설명했다.

이외에도 삼성 파운드리는 EDA 3사와 실리콘 포토닉스 설계 검증, 고속 테스트와 결함 진단, 아날로그 회로의 신뢰성 분석 기술 등에 있어 협력한다.

박진형 기자 jin@etnews.com

Copyright © 전자신문. 무단전재 및 재배포 금지.

- 하반기 신차 2대 중 1대는 '전기차'…캐즘 돌파 승부수

- 당정, 민생지원금 '전 국민' 지급 결정…세입경정 절차도 돌입

- 엔비디아가 투자한 휴머노이드의 '눈' LG이노텍이 만든다

- “소재평가부터 화재시험까지”…K-배터리 분석 기지 KETI 오창 센터

- [바이오 USA]글로벌 위상 과시한 K바이오, 세계 관심 한눈에

- [바이오 USA]CDMO 성장 자신한 존림 삼성바이오 대표 “증설·신사업 진출로 성장동력 확보”

- 네이버, 통합 AI 에이전트 핵심 추론모델 공개 임박…데이터 연동해 구글과 차별화

- 용산구, IoT 종량제 봉투 자판기 확대 도입…공급자 중심에서 소비자 눈높이 전환

- 카카오헬스 '파스타', 스트레스·수면까지 담는다…초정밀 건강관리 구현

- 李대통령, G7서 9개국 정상과 회담…외교 무대서 韓 복귀 알려