초미세 공정을 가능하게 한 신기술은?[반도체 나노 경쟁②]

전체 맥락을 이해하기 위해서는 본문 보기를 권장합니다.

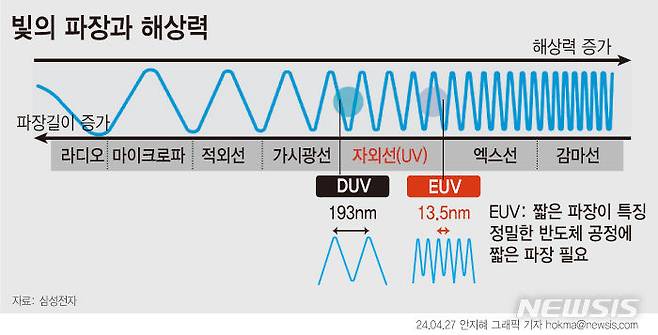

반도체 초미세 공정을 가능하게 한 가장 대표적인 기술 중 하나는 EUV(극자외선) 노광장비다.

노광장비는 설계를 끝낸 회로 패턴을 웨이퍼에 전사하는 리소그래피(Lithography) 공정을 뜻하는데, 그중에서도 EUV를 업계에서는 '세필(細筆)'에 비유한다.

EUV를 반도체 공정에 사용하면 더 세밀한 반도체 회로 패턴을 구현할 수 있다.

이미 EUV는 7나노 이하 파운드리 공정에 핵심 장비로 사용 중이다.

이 글자크기로 변경됩니다.

(예시) 가장 빠른 뉴스가 있고 다양한 정보, 쌍방향 소통이 숨쉬는 다음뉴스를 만나보세요. 다음뉴스는 국내외 주요이슈와 실시간 속보, 문화생활 및 다양한 분야의 뉴스를 입체적으로 전달하고 있습니다.

전력 성능 잡을 新무기 'GAA'

![[서울=뉴시스]인텔 파운드리는 미국 오리건주 힐스보로 R&D 사이트에서 업계 최초 상업용 ‘고개구율(High Numerical Aperture, High NA) 극자외선(Extreme Ultraviolet, EUV)’ 노광장비(리소그래피 스캐너) 조립을 완료했다고 19일 밝혔다. (사진=인텔 제공) photo@newsis.com *재판매 및 DB 금지](https://img1.daumcdn.net/thumb/R658x0.q70/?fname=https://t1.daumcdn.net/news/202404/27/newsis/20240427103109616laph.jpg)

[서울=뉴시스]이인준 기자 = 반도체 초미세 공정을 가능하게 한 가장 대표적인 기술 중 하나는 EUV(극자외선) 노광장비다.

노광장비는 설계를 끝낸 회로 패턴을 웨이퍼에 전사하는 리소그래피(Lithography) 공정을 뜻하는데, 그중에서도 EUV를 업계에서는 '세필(細筆)'에 비유한다.

빛은 파장이 짧아질수록, 해상력(두 물체가 서로 떨어져 있음을 보여줄 수 있는 식별 능력)이 높아지는 특성이 있다. EUV의 파장은 13.5㎚로, 불화아르곤(ArF)을 광원으로 사용하는 기존 노광공정(193㎚)의 14분의 1 미만에 불과하다.

EUV를 반도체 공정에 사용하면 더 세밀한 반도체 회로 패턴을 구현할 수 있다. 도화지에 선을 얇게 그리려면, 붓의 두께를 줄여야 하는 것과 비슷한 이치다.

회로 선폭이 줄면 웨이퍼 한 장 위에 더 많은 회로를 그릴 수 있어 생산능력이 높아지는 효과다. 또 반도체 크기가 작아지면 모바일, 노트북 등 다양한 IT 기기의 '경박단소(輕薄短小·가볍고 얇고 짧고 작음)의 경쟁력에 기여할 수 있다.

나아가 EUV는 단순히 회로를 얇게 그리는 것을 넘어, 더 정밀하게 그릴 수 있는 특징도 있다.

여러 번 덧그리지 않으니, 공정이 간소화하고, 이는 결함 발생을 줄여 수율(합격품의 비율)을 높이는 효과가 있다. EUV 한 대당 수천억원을 호가하는 데도, 반도체 업체들이 납품을 기다리는 이유는 이 때문이다.

전력 흐름 제어도 초미세 공정 기술의 핵심

반도체가 작아지면서 생기는 문제점 중 하나는 전류가 흐르는 통로인 '채널'도 함께 짧아지면서 전류 조절이 어렵게 된다는 점이 있다. 이른바 '단채널(Short Channel)' 현상이다. 일반적으로는 전류의 흐름이 조정이 되는데, 회로 설계 구조 등의 문제로 전류가 과도하게 흐르거나 경계를 넘어 전력이 누수되는 일도 있다. 초미세 공정 도입의 많은 난관 중 하나다.

이를 극복하기 위해 고안된 것이 바로 GAA다. GAA 구조의 트랜지스터는 채널 상-하-좌-우 4면을 게이트가 둘러싸고 있어 전류의 흐름을 더 세밀하게 제어할 수 있다. 이를 통해 누설 전류를 줄여 전력 효율을 높일 수 있게 된다.

GAA는 현재 삼성전자가 전 세계에서 유일하게 3나노 공정에 도입해 양산 중이다. 올해 연내 2세대 3나노 양산이 예정돼 있다. 이어 TSMC, 인텔 등도 차세대 2나노 공정부터는 GAA 기술을 도입한다. 삼성전자는 GAA 주도권 확보를 위해 3세대 GAA도 개발 중이다.

이와 함께 후면전원공급(BSPDN) 기술도 전력 효율을 높이기 위해 업계에서 주목하는 기술이다. 전력 공급선을 뒤쪽에 배치해 회로의 복잡도를 줄여 웨이퍼 상단의 활용률을 높일 수 있다. 또 전력 분포 상황을 개선해, 발열 관리에도 유리하다.

인텔은 업계 최초의 후면 전력 설루션인 '파워비아'를 올해 양산하는 '20A'(2나노급) 공정에 적용한다는 계획이다. TSMC도 내년부터 양산하는 2나노 반도체 생산에 적용을 검토 중인 것으로 알려졌다. 삼성전자도 2나노 공정부터 GAA에 적용한 나노시트(Nanosheet) 기술과 후면전원공급 기술을 통합하기 위한 연구를 진행하고 있다.

![[서울=뉴시스]트랜지스터의 구조 변화에 따른 성능(Performance)과 소비 전력 (Power) 개선. (사진=삼성전자 뉴스룸 제공) photo@newsis.com *재판매 및 DB 금지](https://img3.daumcdn.net/thumb/R658x0.q70/?fname=https://t1.daumcdn.net/news/202404/27/newsis/20240427103110191xymd.jpg)

☞공감언론 뉴시스 ijoinon@newsis.com

Copyright © 뉴시스. 무단전재 및 재배포 금지.

- '최민환과 이혼' 율희, 어깨에 18㎝ 문신…물오른 미모

- 개그우먼 김주연 "하혈 2년에 반신마비…홀로 신병 앓았다"

- 'AOA' 초아 "아이돌 끝나니 설 자리 없어" 토로

- 나나, 전신타투 거의 다 지웠다…화끈한 수영복 자태

- 박위♥송지은, 10월9일 결혼 "웨딩드레스 입으니 실감나"

- 유재환, 음원 사기 피해자 170여명…임형주도 당했다(종합)

- 성인방송 뛰어든 중국 미녀 변호사…"월급 4배 벌어"

- 고은아 "전 남편, 출산 후 폭행…4살 아들 홀로 키워"

- "임신 NO"…한예슬, 결혼설 부인 3개월만 혼인신고

- 결혼 앞둔 여교사…11살 제자와 부적절 관계 '들통'