첨단 패키징 학술대회 내달 5~6일 개최…'3D-칩렛' 기술 방향 제시

전체 맥락을 이해하기 위해서는 본문 보기를 권장합니다.

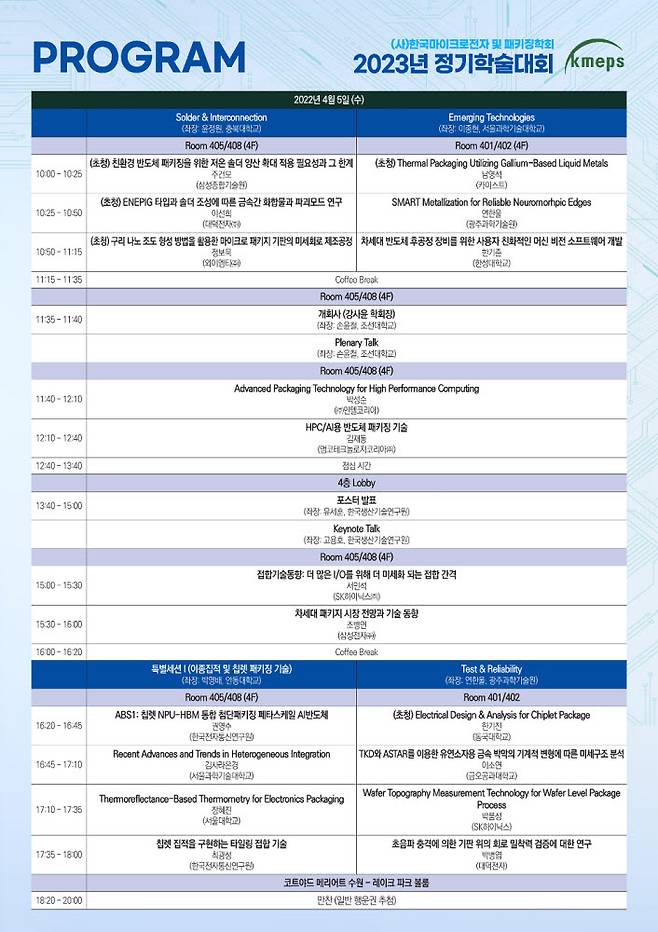

한국마이크로전자·패키징학회(KMEPS)는 다음 달 5일부터 6일까지 경기 수원컨벤션센터에서 '2023년 첨단 패키징 기술 춘계학술대회'를 개최한다.

행사는 5·6세대(G) 통신, 인공지능(AI), 사물인터넷(IoT) 등 고성능 기기에 활용되는 첨단 반도체 기술과 이종집적·칩렛 등 차세대 패키징 연구 동향을 공유한다.

이 글자크기로 변경됩니다.

(예시) 가장 빠른 뉴스가 있고 다양한 정보, 쌍방향 소통이 숨쉬는 다음뉴스를 만나보세요. 다음뉴스는 국내외 주요이슈와 실시간 속보, 문화생활 및 다양한 분야의 뉴스를 입체적으로 전달하고 있습니다.

한국마이크로전자·패키징학회(KMEPS)는 다음 달 5일부터 6일까지 경기 수원컨벤션센터에서 '2023년 첨단 패키징 기술 춘계학술대회'를 개최한다.

행사는 5·6세대(G) 통신, 인공지능(AI), 사물인터넷(IoT) 등 고성능 기기에 활용되는 첨단 반도체 기술과 이종집적·칩렛 등 차세대 패키징 연구 동향을 공유한다.

김재동 엠코테크놀로지코리아 본부장과 박성순 인텔코리아 이사가 기조연설을 맡아 AI 반도체, 데이터센터, 서버 등에 사용되는 칩렛과 하이브리드 본딩 기술 등을 소개한다.

칩렛은 웨이퍼 개별 칩(다이) 여러 개를 연결한 반도체 칩 구조다. 초미세 공정 한계를 극복하고 반도체 성능을 향상할 방안으로 꼽히고 있다.

칩과 칩을 연결하는 돌기(범프) 없이 직접 접합하는 하이브리드 본딩 역시 전기신호 밀도를 크게 높일 수 있어 주목받는다.

조병연 삼성전자 수석은 글로벌 주요 업체의 반도체 패키징 적용 제품을 분석하고 삼성의 첨단 패키징 기술 로드맵을 발표한다. 서민석 SK하이닉스 박사는 반도체와 기판 사이 간격 감소에 따른 접합 기술 발전 방향을 소개한다.

학술대회에서는 이종집적·칩렛 패키징 특별 세션도 열린다. 권영수 한국전자통신연구원(ETRI) 박사와 김사라은경 서울과학기술대 교수, 장혜진 서울대 교수 등이 각각 신경망처리장치(NPU)와 고대역폭메모리(HBM) 패키징을 통한 페타스케일(초당 1000조번 연산) AI반도체와 타일링 접합으로 구현한 칩렛 집적 기술, 광학 측정 방식을 통한 소자 열전도 특성 분석 등을 공개한다.

칩과 기판을 연결해 전기 신호를 전달하는 접합 공정 소재 솔더볼 연구 결과도 발표된다. 이선희 대덕전자 그룹장은 구리 함량 비율과 팔라듐(Pd) 도금 상태 등 최적의 솔더 접합 방안을 제시하고, 주건모 SAIT 박사와 장동민 삼성전자 수석은 친환경 반도체 패키징을 위한 저온 솔더 필요성을 제시한다.

한기진 동국대 교수는 칩렛 호환성 확대를 위한 인터페이스 표준인 UCIe 표준 동향과 기술 과제를 소개한다. 임재영 한양대 교수는 칩렛 반도체 패키징 설계 최적화 방안을 발표한다. 정세영 엔터리움 대표는 고방열 소재와 전자파방해(EMI) 차폐 소재 기술을 소개한다.

송윤섭기자 sys@etnews.com

Copyright © 전자신문. 무단전재 및 재배포 금지.

- 삼성 스마트홈 전초기지 '엑스-홈' 가동

- 반도체 수장 내달 방미...對中 규제 해법 찾나

- 현대캐피탈, 중고차 플랫폼 하반기 구축

- 기업 10곳 중 7곳, 오픈소스 SW 쓴다

- 정보 보안 산업·인력 분류 기준 현실 반영 못해...정확한 산업 전략 못 짠다

- 엘앤에프, 대구 양극재 3공장 7월 완공…자사 최대 공장, 테슬라 수요 대응

- "스마트홈 수요 잡아라" 가전·통신 '매터' 적용 확산

- '애플 효과 주목' LX세미콘, 아이폰15에 DDI 공급…LGD·BOE와 협력

- '수소발전입찰시장위원회' 내달 뜬다

- [2023년 전자신문 독자위원회 1차 회의] "생산가능인구 감소 화두 제시 시의적절"